SPIN2 - Debug LOGIC

Grafische DEBUG-Anzeigen (Theorieteil)

DEBUG-Nachrichten können spezielle grafische DEBUG-Anzeigen aufrufen (z.B. LOGIC, SCOPE, PLOT u.a.), die in das Werkzeug eingebaut sind. Diese grafischen Anzeigen erscheinen in einem eigenen Fenster.

Einmal instanziiert, können die Darstellungen kontinuierlich mit verschiedenen Datentypen versorgt werden, um animierte Visualisierungen zu erzeugen. Bis zu 32 grafische Fenster können gleichzeitig versorgt und angezeigt werden.

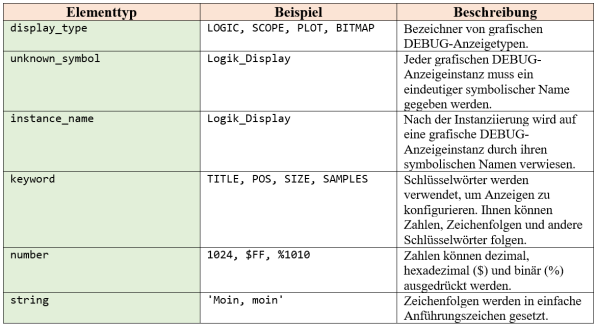

Wenn eine DEBUG-Nachricht ein Backtick-Zeichen (`) (ASCII $60) enthält, wird eine Zeichenfolge, die alles vom Backtick bis zum Ende der Nachricht enthält, an den grafischen DEBUG-Anzeigeparser gesendet. Der Parser sucht nach mehreren verschiedenen Elementtypen und behandelt alle Kommas als Leerzeichen:

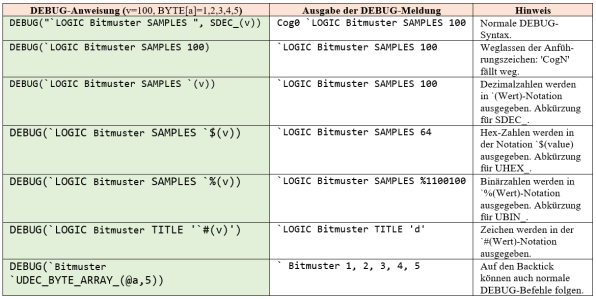

Bevor wir uns damit befassen, wie all dies zusammenpasst, müssen wir einige spezielle Darstellungen bei der DEBUG-Display-Syntax durchgehen.

Diese Syntax wird aufgerufen, wenn das erste Zeichen in einer DEBUG-Anweisung der Backtick ist. Dies bewirkt, dass alles in der DEBUG-Anweisung als Zeichenfolge betrachtet wird, außer wenn nachfolgende Backticks als 'Escape'-Zeichen fungieren, um normale oder abgekürzte DEBUG-Befehle zu ermöglichen.

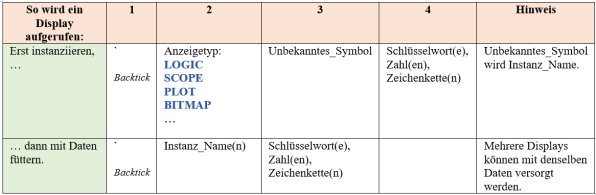

Die Erstellung grafischer DEBUG-Displays erfolgt in zwei Schritten:

a - DEBUG-LOGIC Instanziierung

b - DEBUG-LOGIC Eingabe (feeding)

Schauen wir uns jetzt ein kleines Beispiel mit dem Anzeigetyp LOGIC an.

Übung 1 - DEBUG-LOGIC -> Einfaches Bitmuster erzeugen

In einer einfachen Übung wird ein erster Zugang zum grafischen Teil des DEBUG-Befehls gesucht. Gestartet wird mit dem Anzeigetyp LOGIC. Mit seiner Hilfe ersparen wir uns den Einsatz eines Oszilloskops.

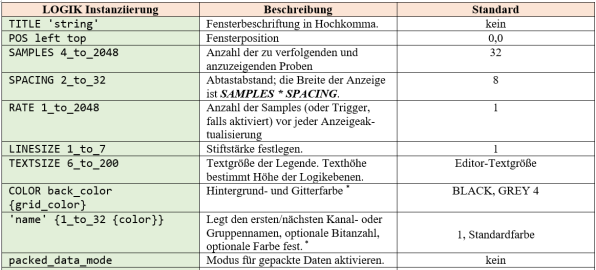

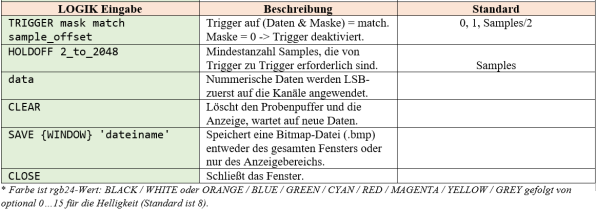

Dafür stehen im Instanziierungs-Bereich verschiedene Instruktionen bereit (s. Abb. 4a), die ergänzt werden durch Instruktionen, die bei der "Datenfütterung" angewendet werden können (s. Abb. 4b).

Mit den Befehlen aus diesen beiden Instruktionsblöcken (Instanziierung, Feeding) kann die grafische Debug-Anzeige LOGIC verändert und an gegebene Wünsche angepasst werden.

| Übung 1 - DEBUG LOGIC -> Einfaches Bitmuster erzeugen | |

| Material |

|

| Aufgaben |

|

Das Programm Bitmuster.spin2

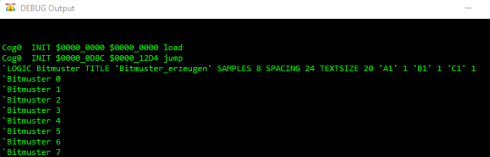

DEBUG - Output Fenster

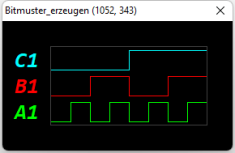

DEBUG - LOGIC Fenster

Wie arbeitet das Programm Bitmuster.spin2 ?

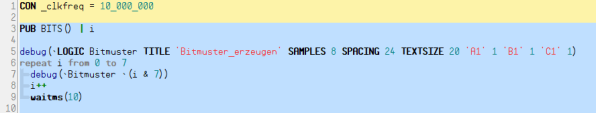

Die eingestellte Taktfrequenz muss, damit überhaupt der Debugger aufgerufen werden und arbeiten kann, größer oder gleich 10 MHz sein. Dies ist in Programmzeile 1 umgesetzt.

Das Hauptprogramm Bits() enthält nur fünf Programmzeilen. Der Graphikteil LOGIC wird in Programmzeile 5 instanziiert; die Fensterbeschriftung ist TITLE 'Bitmuster_erzeugen', das SPACING ist auf 24 gesetzt, damit wird die Zeitachse (Rechtsachse in der Abbildung) gestreckt.

Mit 3 Bits lassen sich insgesamt acht verschiedene Zustände erzeugen, deshalb wird SAMPLES auf 8 festgelegt.

Die Wiederholungsschleife wird achtmal durchlaufen (lokale Variable i). Der aktuelle Zählerstand von i wird binär im Fenster Bitmuster_erzeugen dargestellt.

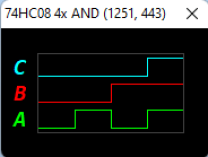

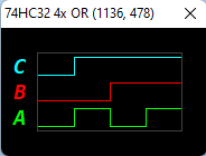

Übung 2 - DEBUG LOGIC -> Wahrheitstafeln von Gattern aufnehmen

In dieser Übung wird gezeigt, wie man die Wahrheitstabelle logischer Gatter mit Hilfe des Propeller P2 aufnehmen und graphisch darstellen kann. Das geht ohne Einsatz eines Oszilloskops und wird über ein SPIN2 Programm und dem Einsatz eines grafischen debug-Befehls erreicht.

| Übung 2 - DEBUG LOGIC -> Wahrheitstafel NAND Gatter | |

| Material |

|

| Aufgaben |

|

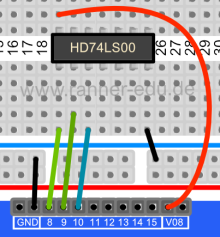

Schaltskizze

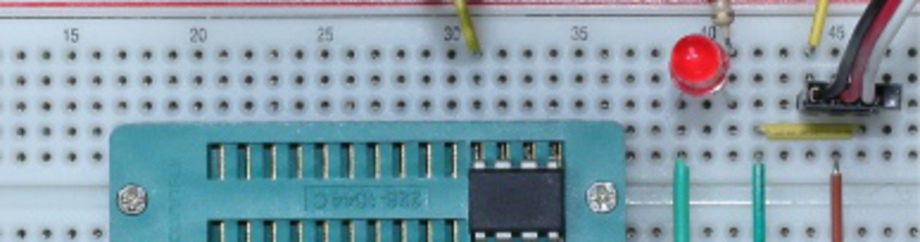

Abb. 7

Aufbau auf einem P2-Edge Breadboard. Jedes andere Breadboard ist ebenfalls geeignet. Die Spannungsversorgung des IC erfolgt hier mit 3,3V vom Breadboard.

Bei TTL-Gattern mit 5V Versorgungsspannung müssen die Spannungspegel für den Propeller P2 (3,3V) unbedingt angepasst werden, damit der Controller nicht beschädigt wird.

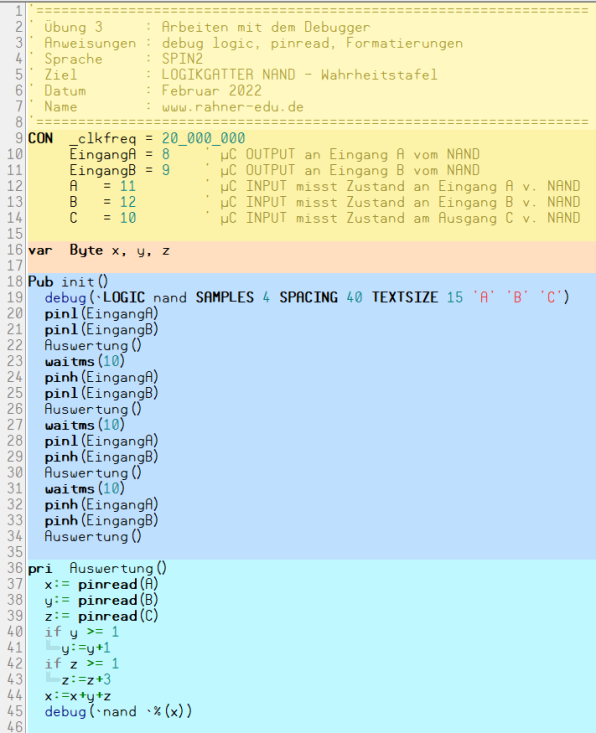

Das Programm debug_logic_nand.spin2

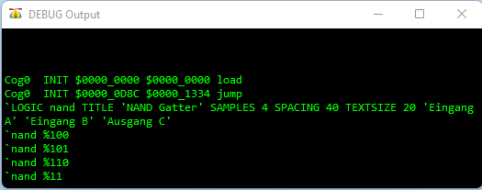

Anzeige im Debug-Output-Fenster

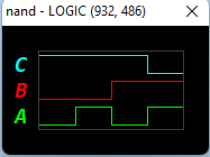

Anzeigen im Debug-LOGIC-Fenster