Entwurfstechnik Halbleiterschaltungen

3 - Transistoren: BJT – JFET – MOSFET

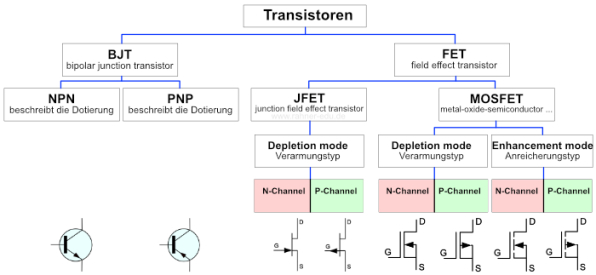

Das folgende Baumdiagramm verdeutlicht, welche Vielfalt an Transistortypen es heute im Markt gibt. Wenn man also von Transistoren spricht, sollte man etwas genauer ausführen, um welchen Typ es sich eigentlich handelt.

3.1 - Bipolar Junction Transistor (BJT) - Theorieteil

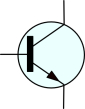

Ein bipolar junction transistor ist, wie der Name schon andeutet, ein Transistor, in dem sowohl negative als auch positive Ladungsträger zum Stromtransport beitragen. Es gibt npn- und pnp-Typen, wobei die Buchstaben die Reihenfolge der Dotierungsträger der Schichtung bezeichnen. Die nach außen geführten Anschlüsse werden als Kollektor (C), Basis (Basis) und Emitter (E) bezeichnet.

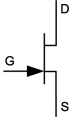

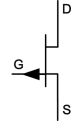

Die Schaltsymbole

Gesteuert wird ein BJT mittels eines Stromes über die Basis (Stromsteuerung). Dazu muss der Basiswiderstand berechnet werden (s. Entwurfstechnik Halbleiterschaltungen).

3.2 - FET oder Field-Effect-Transistor - Theorieteil

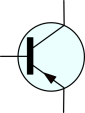

Hier handelt es sich um unipolare Transistoren, bei denen nur ein Ladungstyp am elektrischen Strom beteiligt ist; bauartabhängig entweder Elektronen oder Defektelektronen. Auch dieser Transistor verfügt über drei Anschlüsse: Source (S), Gate (G) und Drain (D).

Im Gegensatz zum BJT benötigt er keinen Steuerstrom, sondern eine Steuerspannung. Das Gate (G) ist die Steuerelektrode; sie wirkt wie ein kleiner Kondensator, dessen elektrisches Feld Ladungsträger aus dem Leitungskanal zwischen Source (S) und Drain (D) verdrängt oder verdichtet. Damit ist das Gate praktisch sehr hochohmig.

Die Schichtung von bipolaren Transistoren (NPN, PNP) findet sich auch bei FETs wieder; es gibt den sog. N-Kanal- und P-Kanal-FET.

Es gibt zwei Familien von Feldeffekt-Transistoren: den Junction-FET (JFET) und den Metal-Oxide-Semiconductor FET (MOSFET), der früher als insulated-gate-FET (IGFET) bezeichnet wurde.

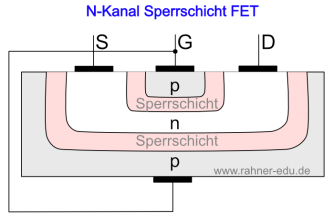

3.3 Sperrschicht-Feldeffekt-Transistor (JFET) - Theorieteil

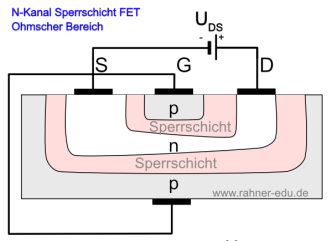

Die n-Zone ist schwächer dotiert als die beiden p-Zonen. Im unbeschalteten Zustand bilden sich zwischen den Halbleiterzonen sogenannte Sperrzonen aus, die vorrangig in die schwächer dotierte n-Zone hineinwachsen und damit einen Kanal negativer Ladungsträger bilden, an deren beiden Enden sich die Elektroden S (Source) und D (Drain) befinden (s. Abb. 3).

Legt man zwischen D und S eine Spannung UDS an (Pluspol am Drain-Anschluss) und lässt G unbeschaltet bzw. verbindet ihn mit S (s. Abb. 4), dann ändert sich die Geometrie der Sperrschichten. Da der Drainanschluss mit dem Pluspol der Energiequelle verbunden ist, werden die Elektronen zum Pluspol der Energiequelle abgesaugt und die Sperrschicht vergrößert. Der zwischen S und D fließende Drainstrom ID wird mit größer werdender Spannung UDS immer geringer, da sich die Sperrschichten vergrößern.

- ID und UDS verhalten sich in diesem Bereich nahezu proportional zueinander; deshalb nennt man diesen Bereich „Ohmscher Bereich“.

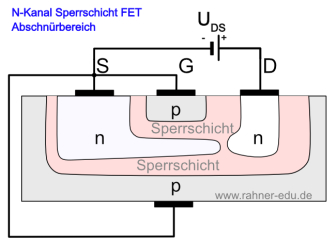

Erhöht man UDS weiter, berühren sich die beiden Sperrschichten und schnüren den n-Kanal ab (s. Abb. 5). Ladungsträger können durch diese schmale Abschnürstelle diffundieren, der Drainstrom fließt weiter und damit verbreitert sich die Abschnürstelle und wirkt dem Diffusionsstrom entgegen. Auf diese Art koppelt sich der Diffusionsstrom selbst zurück und begrenzt sich. Zwischen S und D stellt sich ein nahezu konstanter Strom ID ein. Diesen Bereich nennt man auch Abschnürbereich.

- Im Abschnürbereich bleibt der Drainstrom ID auch bei Erhöhung von UDS nahezu konstant.

Ab einem bestimmten Grenzwert von UDS steigt ID weiter an und führt schließlich zum Durchbruch zwischen Gate und n-Kanal; der Transistor wird zerstört (Breakdown-Bereich).

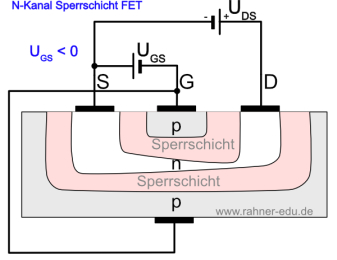

Legt man zwischen G und S eine negative Spannung UGS an, dann verbreitern sich die Sperrzonen und der n-Kanal verengt sich. Physikalisch bedeutet das, dass sich der Widerstand vergrößert hat mit der Folge, dass die Abschnürung bei einer geringeren Spannung UDS eintritt und der Maximalwert von ID geringer ausfällt.

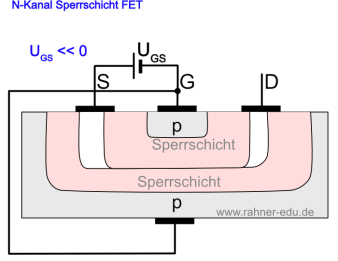

Eine weitere Erhöhung der Spannung UGS führt dazu, dass ab einem bestimmten Wert überhaupt kein Drainstrom ID mehr fließt.

- Ein n-Kanal FET sperrt nur dann, wenn sein Gate negativ vorgespannt ist.

- Der Sperrschicht FET ist selbstleitend, das heißt, wenn keine Spannung zwischen Gate und Source anliegt (UGS = 0), fließt ein maximaler Drainstrom ID durch den FET bei anliegender Spannung UDS; die Sperrschichten behindern den Stromfluss nur unwesentlich.

Die Schaltsymbole

Welche Grenzwerte gilt es zu beachten?

Im Datenblatt eines FET finden sich neben den absoluten Grenzwerten auch Informationen über seine elektrischen Eigenschaften. Uns interessieren:

Absolute Grenzwerte

- Drain-Gate Voltage (UDG)

- Gate-Source Voltage (UGS)

- Forward Gate Current (Durchlassstrom Gate) (IGF)

- Total Device Dissipation (Gesamtverlustleistung) (PD)

OFF-Charakteristik

- Gate-Source Cut-off Voltage (UGS(off))

Die Cutoff- oder Pinch-off Spannung eines FET ist die Spannung UGS,off, die ihn abschaltet. Bei einem N-Kanal FET liegt sie unter 0 Volt, bei einem P-Kanal FET darüber.

ON Charakteristik

- Zero-Gate Voltage Drain Current (IDSS)

Steigt die Gatespannung bei einem N-Kanal FET an, fällt der Drainstrom immer weiter ab und versiegt ab einer bestimmten Größe ganz. Der Wert von IDSS weist den maximalen Strom aus, den ein FET bei UGS = 0 im Toleranzbereich UDS erreichen kann.

Übung 1 – Der selbstleitende n-Kanal JFET - MO

| Übung 1 - Der selbstleitende N-Kanal JFET - MO | |

|

Material |

|

|

Aufgaben |

|

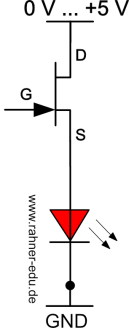

Schaltskizze

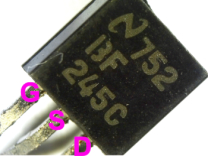

Pinbelegung BF 245

Beobachtungen

Von 0 V bis ca. 1,6 V leuchtet die LED nicht; ab UDS = 1,7 V beginnt sie zu leuchten und ihre Helligkeit nimmt mit steigender Spannung UDS bis auf ca. 3,2 V stetig zu. Eine weitere Erhöhung der Spannung UDS auf maximal 15 V führt nach optischem Eindruck zu keiner weiteren Steigerung der Helligkeit.

Übung 2 – Kennlinienaufnahme zweier n-Kanal JFET - MO

| Übung 2 - Kennlinienaufnahme zweier n-Kanal JFET - MO | |

|

Material |

|

|

Aufgaben |

|

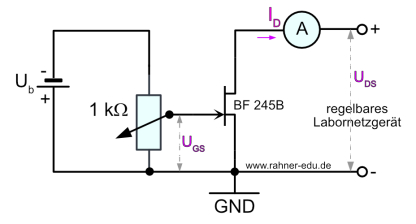

Schaltskizze

Die Batteriespannung Ub sollte ca. 3 Volt (zwei AA-Batterien in einem Batteriehalter) oder ca. 5 Volt (drei AA-Batterien) betragen.

Graphische Auswertung der Messreihe

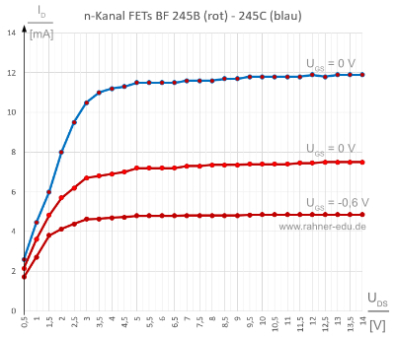

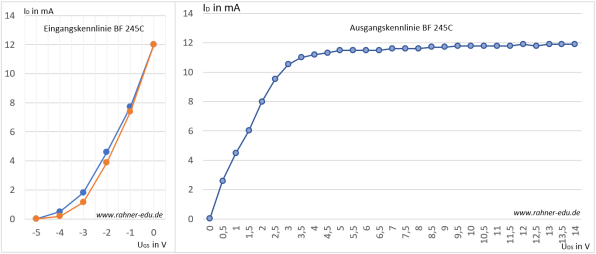

Die gemessenen Daten werden in eine Excel-Tabelle übertragen und dann graphisch umgesetzt. Für die beiden JFETs (BF 245B und BF 245C) ergeben sich folgende Kennlinien:

Der Drain-Strom für die beiden untersuchten JFET-Typen wird im Datenblatt für den

- BF 245B mit 6 mA < IDSS < 15 mA, bei UDS = 15 V, UGS = 0 V

- BF 245C mit 12 mA < IDSS < 25 mA, bei UDS = 15 V, UGS = 0 V

angegeben. Gemessen wurden für den vorliegenden

- BF 245B IDSS = 7,5... mA, bei UDS = 15 V, UGS = 0 V

- BF 245C IDSS = 12 mA, bei UDS = 15 V, UGS = 0 V

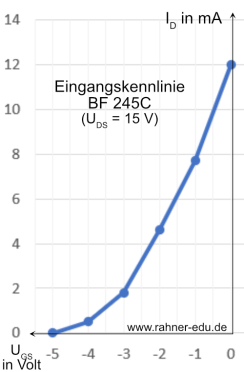

Zur Mathematik der Eingangskennlinie

Die charakteristische Größe der Eingangskennlinie ist die pinch-off Spannung UPoff. Wird sie unterschritten, sinkt der Drainstrom auf fast 0 mA ab; es fließt tatsächlich aber noch ein geringer Reststrom im nA Bereich.

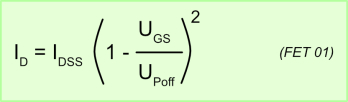

- Für UGS > UPoff gilt folgender mathematische Zusammenhang bei n-Kanal FETS, der seine Eingangskennlinie beschreibt:

- Trägt man die Messwerte aus Übung 2 in Formel FET 01 ein und errechnet ID, dann bekommt man die theoretische Eingangskennlinie des FET. Für den benutzten BF 245C ergibt sich folgender Verlauf:

Die orangenfarbige Kurve zeigt die mathematisch berechnete Eingangskennlinie.

Steilheit eines FET

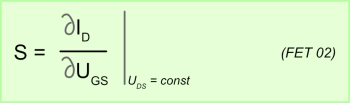

- Die Steilheit eines FETs ist definiert als die Steilheit seiner Eingangskennlinie:

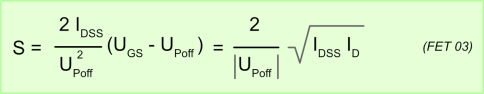

- Differenziert man Gleichung FET 01 partiell nach UGS, erhält man aus FET 01 die neue Gleichung FET 03:

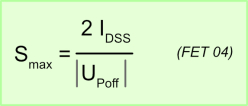

- Die maximale Steilheit Smax ergibt sich für den Fall ID = IDSS und errechnet sich aus der Ableitung von FET 03:

- Die maximale Steilheit Smax liegt i.A. zwischen 1 mS und 1 S. Für den von mir benutzten Transistor BF 245C ergibt sich nach Formel FET04 ein Wert von ca. 4 mS. Nach Datenblatt für diesen Transistortyp soll der Wert zwischen 3 mS und 6,5 mS liegen.

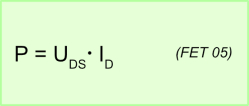

Maximale Verlustleistung (total power dissipation)

- Die Verlustleistung eines FET wird erzeugt von der am Transistor anliegenden Spannung UDS und dem durch ihn hindurchfließenden Strom ID; dadurch wird das Bauteil erwärmt. Bei einem FET in Sourceschaltung berechnet sich die Verlustleistung P nach:

Nach Datenblatt liegt die maximale Verlustleistung eines Transistors vom Typ BF 245 bei 300 mW. Gleichung FET 05 ergibt bei einer anliegenden Spannung von UDS = 15 V einen maximalen Drainstrom von ID = 20 mA.

- Aber Achtung: manchmal kann die maximale Verlustleistung nur unter der Bedingung ausgenutzt werden, dass man den Transistor ausreichend kühlt.

Zusammenfassend kann man sagen:

- Für eine gleichbleibende Spannung UGS erhält man eine Kennlinie, die der IC-UCE-Kennlinie eines BJT für konstanten Basisstrom IB sehr ählich ist. Die Gatespannung entspricht dabei dem Basisstrom.

- Die JFET-Kennlinien zeigen bis zur Kniespannung (Knick) einen nahezu linearen Verlauf (Ohmscher Bereich).

- Im ohmschen Bereich wirkt der n-Kanal wie ein veränderlicher Widerstand.

- Je größer der Betrag von UGS ist, desto größer ist der Widerstand.

- Die Kniespannung der Kennlinie ist die Spannung, bei der der n-Kanal im Drainbereich abgeschnürt wird.

- Je größer der Betrag von UGS, desto kleiner ist die Kniespannung und der Drainstrom.

- Die pinch-off Spannung UPoff schnürt den ganzen Kanal ab; es fließt kein Strom mehr.

(letzte Änderung: Feb. 2021)