Digitaltechnik - 4b

4.1 - Flipflops

Neben Gattern sind Flipflops die wichtigsten Grundelemente digitaler Schaltungen. Sie kennen zwei stabile Ausgangszustände (HIGH oder LOW) und ändern den jeweiligen Zustand nur, wenn eine bestimmte Eingangsinformation vorliegt. Solche Schaltungen werden auch als bistabile Kippstufen bezeichnet. Mit ihnen lässt sich ein Bit beliebig lange speichern, vorausgesetzt, die Betriebsspannung wird nicht abgeschaltet.

Einsatzgebiete von Flipflops sind Speicher, Zähler, Schieberegister und Frequenzteiler.

Es gibt eine Vielzahl verschiedener Flipflops, die alle auf dem RS-FF basieren und sich nur unterscheiden durch:

- den strukturellen Aufbau

- die Taktabhängigkeit

- die Art der Ansteuerung

- die Anzahl und Wirkung der Eingänge

Alle in diesem Kapitel angesprochenen Simulationsprogramme können für den unterrichtlichen oder privaten Bedarf von mir per E-Mail gegen einen Unkostenbeitrag bezogen werden.

4.2 – Nicht getaktetes RS-Flipflop (Grund-Flipflop)

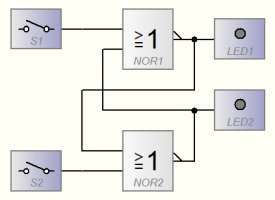

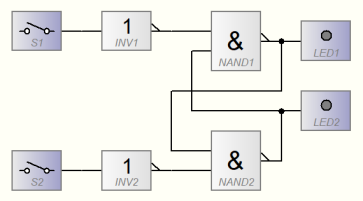

Die einfachste Ausführung eines nicht getakteten Flipflops, sogenannte RS-Flipflops (RS-FF), bestehen aus zwei NAND- bzw. zwei NOR-Gattern.

Damit die Schaltungsbelegung für ein NOR- und ein NAND- RS-Flipflop identisch ist, muss der Aufbau bei einem NAND-Flipflop etwas modifiziert werden (siehe Abb. 2). Beiden Eingängen wird in diesem Fall ein Inverter vorgeschaltet.

Das nicht getaktete RS-FF verfügt über zwei Eingänge: R (S1 in Abb. 2) - steht für RESET oder „Zurücksetzen“ und S (S2 in Abb. 2) – steht für SET oder „Setzen“ des Ausgangs Q an NAND1. Dieser Zustand ändert sich nur dann, wenn der Eingang R auf HIGH oder 1 gezogen wird und gleichzeitig der Eingang S LOW oder 0 ist.

- Der Zustand R = S = 1 oder HIGH ist nicht definiert und muss schaltungstechnisch vermieden werden.

Zieht man den Setzeingang (S) auf HIGH, kippt das Flipflop in die stabile Lage Q = 1. Legt man an den Eingang R (Reset) eine 1, wird dasFlipflop zurückgesetzt oder Q = 0. Beide Lagen sind statisch stabil.

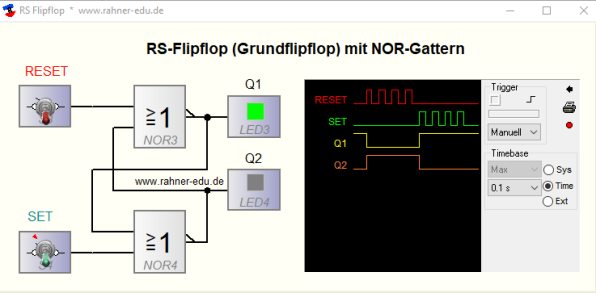

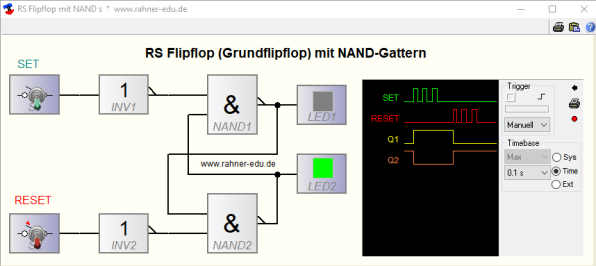

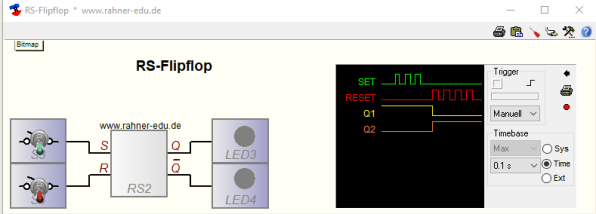

4.2.1 – Simulationsschaltungen zu nicht getakteten Grund-Flipflops

Zu den beiden RS-Flipflops mit NOR- bzw. NAND-Gattern gibt es je eine Simulationsschaltung, die zu Übungszwecken eingesetzt werden kann. Das Erstellen und Lesen von Zeitdiagrammen kann hier vertiefend eingeübt werden.

Die Programmoberfläche des Simulationsprogramms "RS_FF_2.exe" unterscheidet sich nur im Schaltungsaufbau von "RS_FF_1.exe". Die Wirkungsweise ist ähnlich.

Ergebnisse

- Liegt Q1 auf HIGH und der R-Eingang auf 0, dann haben Pegeländerungen am S-Eingang keine Auswirkungen auf Q1 - er verbleibt auf HIGH.

- Liegen Q1 und S auf LOW, haben Pegeländerungen am R-Eingang keine Auswirkungen auf Q1.

Im weiteren Verlauf wird der diskrete Aufbau eines RS-Flipflops aus NAND- und NOR-Gattern durch einen fertigen SR-Flipflop Baustein ersetzt. Die Schaltung aus Abb. 1 vereinfacht sich zu:

4.2.2 – Simulationsschaltungen zu getakteten Grund-Flipflops

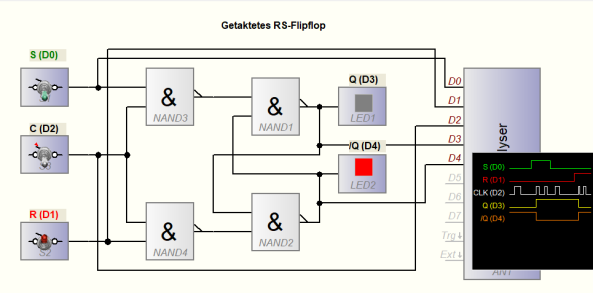

Ersetzt man in einem NAND-Flipflop (siehe Abb. 2) die beiden Inverter durch je ein NAND-Gatter, hat man bei geeigneter Verdrahtung ein getaktetes RS-Flipflop (s. Abb. 5a).

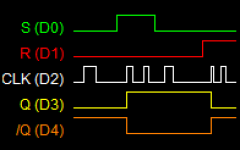

Abb. 5a – Getaktetes RS-FF. S (D0) ist der Set-, R (D1) der Reset- und C (D2) der Takt(CLOCK)-Eingang. D3 entspricht dem Ausgang Q, D4 entsprechend /Q. Das Zeitdiagramm - aufgenommen mit einem Logikanalysator - dokumentiert das Verhalten dieses Flipflops. Auf die Darstellung von /Q wurde hier verzichtet.

Es übernimmt immer nur zu bestimmten Zeitpunkten mit Hilfe einer Taktsteuerung (Eingang C(LOCK) oder D2 auch als Takt-, Freigabeeingang oder Enable bezeichnet) die an den Eingängen S und R anliegenden Signale. Solche Schaltungen bezeichnet man auch als Latch oder Gated Latch.

Hauptmerkmal eines solchen Latch ist, dass sich die Ausgangssignale Q und /Q im Zeitintervall, in dem das Enable- oder Taktsignal auf HIGH gezogen ist, ändern können (s. Abb. 5a). Flankengetriggerte Flipflops zeigen dagegen ein anderes Schaltverhalten.

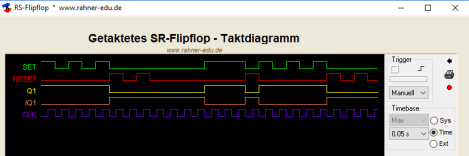

Das nachfolgende Taktdiagramm basiert auf einem getakteten SR-Flipflop, dessen Eingangsdaten aus einem ROM gelesen werden.

Die Daten am S- und R-Eingang werden im Simulationsprogramm über ein ROM an die Eingänge eines SR-Flipflops gelegt und Eingangs- wie Ausgangsimpulse mit einem Logikanalyser sichtbar gemacht. Im Simulationsprogramm lassen sich die im ROM hinterlegten Daten ändern.

- Bei einem Auffangflipflop (Latch) hat die Information an den beiden Vorbereitungseingängen S und R des Grundflipflops keinen Einfluss auf den Ausgang, wenn am Takteingang C eine 0 liegt. Liegt dort eine 1 an, wird die Eingangsinformation an den jeweeiligen Ausgang durchgereicht. Was am Ausgang Q bzw. /Q geschieht, hängt also davon ab, was an R und S anliegt, wenn ein Taktimpuls auf HIGH gezogen wird.

4.3 - Getaktetes D- oder Verzögerungs-Flipflop, D-Latch

Ein D-Flipflop (delay-FF) wirkt als Verzögerungseinheit. Das Eingangssignal erscheint verzögert um einen Taktimpuls am Ausgang Q. Es hat nur einen Signaleingang (s. Abb. 6).

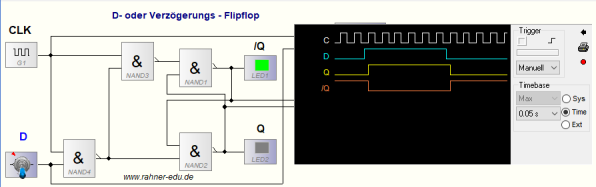

Abb. 6 –Zeitdiagramm eines D-Flipflops. Gestartet wird das Programm über den kleinen roten Knopf unterhalb des Druckers im Zeitdiagrammfenster.

Darin bedeuten: CLK(weiß) -> Takt, D (blau) -> Dateneingabe, Q (gelb) -> Ausgang, /Q (orange) -> invertierter Ausgang.

Der Startbildschirm des Programms zeigt den diskreten Aufbau eines D-Latch aus NAND-Gattern und nicht das Schaltsymbol eines D-Latch.

Nach Programmstart ist /Q HIGH oder 1, Q entsprechend 0; der Eingang D ist auf 0 voreingestellt. Wird D = 1 und geht C auf 1, dann wird Ausgang Q = 1 und verbleibt dort, auch wenn D wieder auf 0 geht. Mit D = 0 wird Ausgang Q mit dem nächsten Taktimpuls (steigende Flanke) von CLK auf 0 gesetzt.

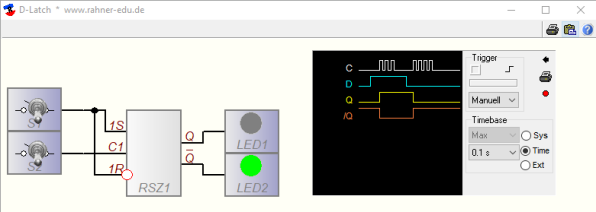

Die Schaltung aus Abbildung 6 lässt sich durch ein zustandsgesteuertes RS-Flipflop ersetzen und vereinfachen.

Abb. 7 - Zustandsgesteuertes RS-Flipflop. Das Zeitdiagramm dieses Bausteins ist identisch mit dem D-FF aus Abbildung 6. Die Eingänge R und /S werden über Schalter 1 (D-Eingang) gesteuert; die Negation an einem der beiden Eingänge (in dieser Schaltung ist es /R) ist wegen des Verbots R = S = 1 notwendig.

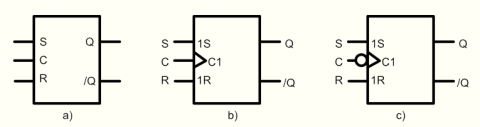

4.4 - Einige Schaltsymbole getakteter RS-Flipflops

Zusammenfassung der Ergebnisse:

- Das Signal zum Setzen oder Rücksetzen eines Flipflops muss nur kurzzeitig am R- oder S-Eingang anliegen; typisch sind ca. 10 ns.

- Ist das Flipflop am Ausgang Q auf 1 gezogen worden, dann haben weitere HIGH-Signale am S-Eingang keinen Einfluss mehr auf den Zustand am Ausgang.

- Ist C auf LOW oder 0, dann wirken sich Pegeländerungen am S- und R-Eingang nicht aus.

- Der Zustand R = S = 1 ist nicht zulässig.

- Eine typische Anwendung ist die Taster- bzw. Schalterentprellung.

Wenn es schaltungstechnisch nicht möglich ist, den Zustand R = S = 1 zu vermeiden, dann muss ein JK-FF (siehe Abschnitt 5 – JK-Flipflop) eingesetzt werden, bei dem diese Kombination zulässig ist.

4.5 – Beschreibung des Verhaltens von Flipflops

Grundsätzlich gibt es zwei unterschiedliche Taktsteuerungsmöglichkeiten, um die an den Eingängen eines Flipflops anliegenden Informationen in den Flipflop zu übernehmen:

- Taktzustandssteuerung oder statische Taktung und

- Taktflankensteuerung oder dynamische Taktung. Die an den Eingängen unmittelbar vor einem Taktübergang anliegenden Daten bestimmen den Ausgangszustand.

Zu 1:

Latches sind taktzustandsgesteuerte Flipflops, bei denen die an den Eingängen anliegende Information sofort an den Ausgang durchgereicht wird, wenn der Taktimpuls oder Enable HIGH ist. Diese Eigenschaft ist für Frequenzteiler oder Zähler nicht brauchbar.

Zu 2:

Bei der Taktflankensteuerung wird zwischen einer steigenden und einer fallenden Flanke unterschieden.

Bei einer Einflankensteuerung (edge-triggered, steigend oder fallend) wird diejenige Information am Eingang in den Flipflop übernommen, die vor der aktiven Taktflanke am Eingang lag. In der Zeit zwischen den aktiven Taktflanken bleibt der Flipflop inaktiv.

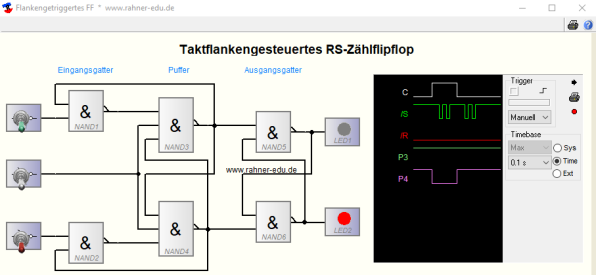

Eine Zweiflankensteuerung (Pulstriggerung) findet man bei einem JK-Master-Slave-Flipflop vor. Das folgende Beispiel eines Taktflankengesteuerten RS-Zählflipflops soll dieses Prinzip näher erläutern:

Die Schaltung besteht aus drei Blöcken: den Eingangsgattern, einem Pufferspeicher und den Ausgangsgattern.

Zustand: C = 0

Die Ausgänge von P3 (NAND3) und P4 (NAND4) sind auf HIGH (siehe Abb. 9), die Eingangsgatter sind geöffnet. Am Eingang des Puffers liegt die invertierte Eingangsinformation. Der Puffer sperrt.

Zustand: Anstieg der Flanke C, C = 1

Mit dem Anstieg der Flanke wird der Pufferspeicher mit der Eingangsinformation gesetzt. P3 oder P4 wird LOW und die Eingangsgatter sperren; gleichzeitig werden die Ausgangsgatter ebenfalls gesetzt. Signalwechsel am Eingang ändern den Pufferspeicher nicht, auch wenn C = HIGH ist (s. Abb. 9).

Mit der fallenden Flanke wird der Ausgangszustand wieder hergestellt.

In getakteten Schaltungen wird zu seiner Beschreibung der Zustand des Ausgangs Q

- vor einem Taktimpuls mit Qn oder Qn und

- nach einem Taktimpuls mit Qn+1 bzw. Qn+1

bezeichnet.

Konsequenterweise bedeutet dann Rn bzw. Rn das Eingangssignal an R vor und Sn+1 bzw. Sn+1 das Eingangssignal an S nach einem Taktimpuls.

Bei flankengetriggerten Flipflops muss die Beschreibung weiter präzisiert werden; zusätzlich muss zwischen

- steigender und

- fallender Flanke

unterschieden werden.

4.6 - JK Flipflop

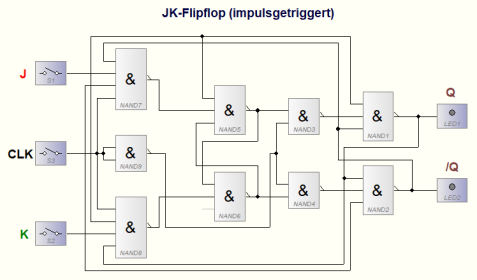

Das JK-Flipflop ist ein sehr häufig eingesetztes Zähl-Flipflop, das den Nachteil eines RS-Flipflop durch Rückführungsleitungen beseitigt. Den Aufbau zeigt Abb. 9a.

Das nachfolgende Impulsdiagramm zeigt die Arbeitsweise des JK-Flipflop.

4.7 - Master-Slave Flipflop

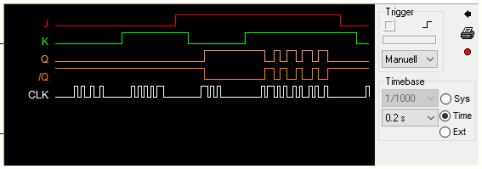

Die nachfolgende Schaltung zeigt den Schaltungsaufbau eines RS-Master-Slave-Flipflops. Wie jedes Master-Slave-FF, setzt es sich aus zwei Grundflipflops zusammen, bei dem die zweite Stufe (Slave) mit einem komplementären Taktimpuls angesteuert wird (s. auch Abb. 9a).

Ein Taktimpuls am C-Eingang trennt zunächst den Master vom Slave; anschließend werden die Eingänge R und S mit dem Master verbunden und so die Eingangsinformation in den Master übernommen. An der Rückflanke des Taktimpulses werden die Eingänge vom Master getrennt und die im Master zwischengespeicherte Information in den Slave übernommen. Sie wird an den beiden Ausgängen Q und /Q angezeigt. Die Ausgänge sind komplett von den Eingängen getrennt; dies wird in Abb. 10 durch die Pegeländerungen am Eingang demonstriert.

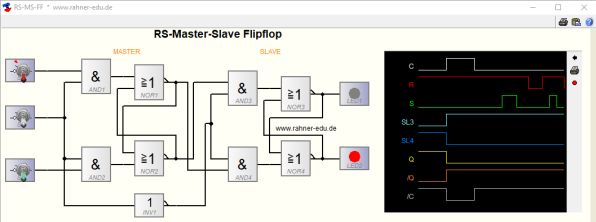

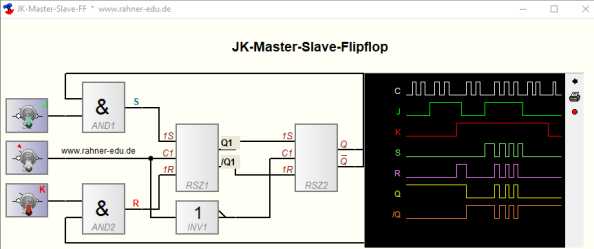

4.8 - JK-Master-Slave Flipflop

Ein sehr universell einsetzbarer und wohl der universellste Flipflop-Typ, der die Unbestimmtheit in der Wahrheitstafel eines RS-Flipflops beseitigt.

Wie arbeitet die Schaltung?

Die vier möglichen Wertekombinationen der Eingangsschalter J und K während eines Taktimpulses kann man Abb. 11 entnehmen. Wir unterscheiden die vier Fälle:

- Fall: J = K = LOW

Daraus folgt, dass S und R identisch Null sind; unabhängig vom Taktzustand behalten Q1 und Q ihren Zustand bei.

- Fall: J = LOW, K = HIGH

Q = LOW: S und R sind LOW; der Ausgangszustand Q bleibt erhalten.

Q = HIGH: wegen K = LOW ist dann auch R = LOW. Wegen J = LOW ist S LOW. Geht C auf HIGH, geht Q1 auf LOW. Geht T wieder auf LOW, wird Q LOW. Für beide Ausgangszustände ist am Ende des Taktes Q auf LOW. Im zweiten Fall wird mit fallender Taktflanke Q auf LOW gesetzt bzw. bleibt auf LOW.

- Fall: J = HIGH, K = LOW

Überlegungen wie im 2. Fall; mit fallender Taktflanke wird jetzt Q auf HIGH gesetzt bzw. bleibt auf HIGH.

- Fall: J = K = HIGH

Die beiden AND-Gatter am Eingang sind offen. Das Flipflop kippt bei jeder fallenden Taktflanke.

Überträgt man das Geschriebene in eine Wahrheitstabelle, dann sieht die für ein JK-Master-Slave Flipflop wie folgt aus:

| J | K | Qn+1 |

| 0 | 0 | Qn |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Qn |

4.9 - T Flipflop

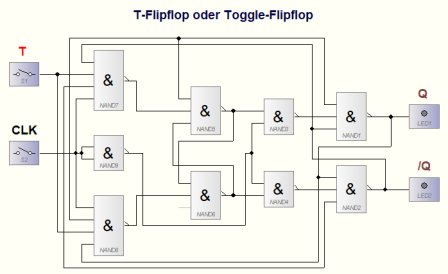

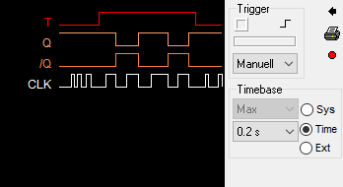

Verbindet man in Abb. 9a die beiden Eingänge, entsteht ein T-Flipflop oder Toggle-Flipflop.

Dem Impulsdiagramm (s. Abb. 13) kann deutlich entnommen werden, dass ein T-FF wie ein binärer Teiler oder Frequenzhalbierer wirkt.

Liegt Eingang T auf LOW, bleibt der vorhandene Zustand am Ausgang Q unverändert.

Wird Eingang T auf HIGH gezogen, ändern sich die Zustände an den Ausgängen Q und /Q mit jeder fallenden Taktflanke des Taktgebers.

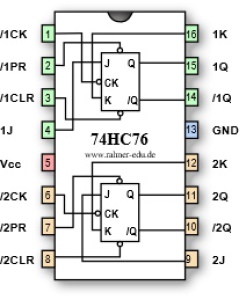

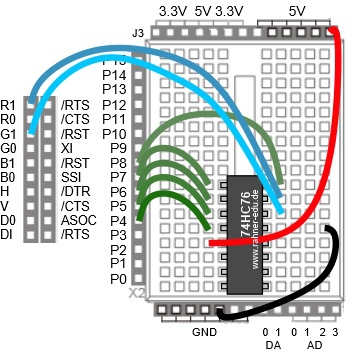

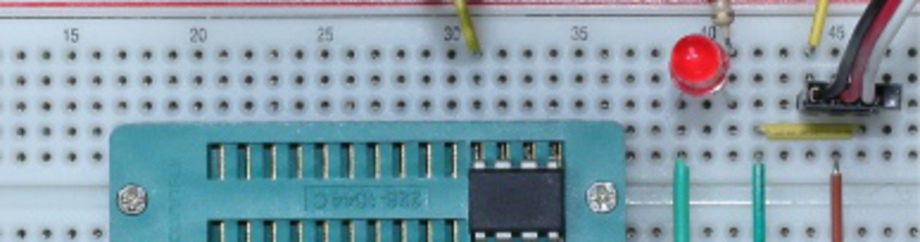

5 - Praktische Übung mit einem IC 74HC76

Die Bedeutung der Abkürzungen

/1CK, /2CK Takteingang (Triggerung über fallende Flanke) /1PR, /2PR Setzeingang (Active LOW) /1CLR, /2CLR Asynchroner Reseteingang (Active LOW) 1J, 2J Dateneingabe: FF1 und FF2 /1Q, /2Q Ausgang des FF (Komplementdarstellung) 1Q, 2Q Ausgang des FF 1K, 2K Dateneingabe: FF1 und FF2 GND Masse, 0V Vcc Versorgungsspannung 3,3V oder 5,0V

| Übungen mit dem IC 74HC76 | |

| Material |

|

| Aufgaben |

|

Die Schaltung

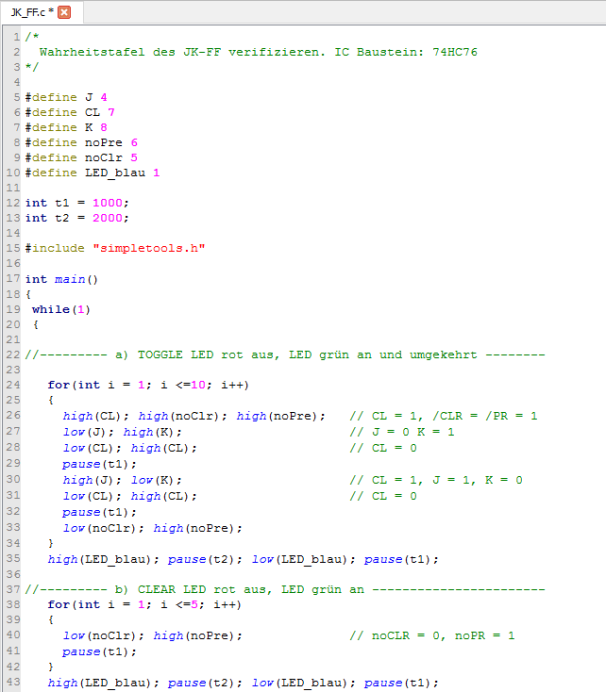

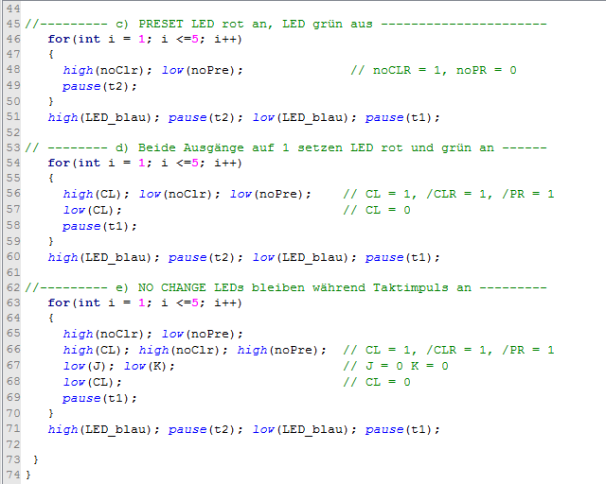

Das Programm JK-FF.c

Was man auch machen könnte

- Das IC 74HC76 enthält zwei JK-FF. Verbindet man die Ausgänge Q und /Q des ersten JK-FF mit den Eingängen J und K des zweiten, erhält man ein JK-Master-Slave-FF (JK-MS-FF). Die steigende Taktflanke schaltet das erste, die fallende das zweite Flip-Flop. Dazu müssen beide Takteingänge über einen Inverter miteinander verbunden sein.