1 - Synchrone serielle Kommunikation

Bei der Kommunikation zwischen verschiedenen IC-Bausteinen spricht man von synchroner Kommunikation, wenn dazu ein CLK-Signal eingesetzt wird, um Sender und Empfängersignal miteinander zu synchronisieren. Beim Senden oder Empfangen von Daten wird so lange gewartet, bis die Kommunikation abgeschlossen ist.

Daten lassen sich auf zwei Arten übertragen: parallel oder seriell. Von beiden Methoden ist die parallele Übertragung die schnellere, benötigt aber auch mehr I/O Leitungen und damit Anschlusspins vom Controller. Bei der seriellen Übertragung werden 1, 2 oder 3 Leitungen und damit Pin des Controllers belegt. Die beiden geläufigen Modi sind die synchrone und asynchrone Datenübertragung. Dabei meint synchron, mit Hilfe von CLK-Impulsen Daten in Blocks zusammengefasst übertragen und asynchron einzeln und unabhängig voneinander.

Allgemein werden viele elektronische Bauteile heute über ein serielles synchrones Interface angesprochen. Es ist deshalb unverzichtbar, ein fundiertes Hintergrundwissen zu haben.

In diesem Kapitel wird mit Hilfe einer BASIC Stamp ein A/D Wandler konfiguriert und die Daten ausgelesen.

Der Befehl PULSOUT

Dieser Befehl erzeugt einen Puls am I/O Pin pin mit der Pulslänge dauer. Mit diesem Befehl erzeugen wir das für die synchrone Kommunikation erforderliche CLK-Signal.

-

PULSOUT pin, dauer

Erklärung der Parameter

pin kennzeichnet den Ausgangspin (0 - 15).

dauer (0 - 65535) gibt die Impulsdauer als Vielfache einer Einheit

an. Für die beiden

BASIC Stamp Module BS1 und BS2 gelten

folgende Werte

| Modul | Zeiteinheit | max. Pulsweite |

| BS1 | 10µs | 655,35ms |

| BS2, BS2pe | 2µs | 131.07ms |

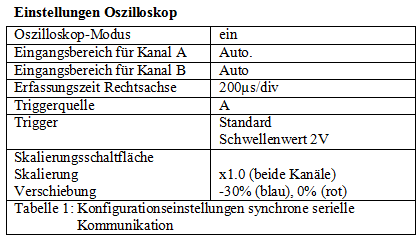

Mit einem kleinen Programm überprüfen wir die Impulsfolge mit dem Oszilloskop. Gib dazu das folgende Programm in den Editor ein und starte es. Entnimm das Signal für das Oszilloskop über P1.

-

DO PULSOUT 1, 210 LOOP

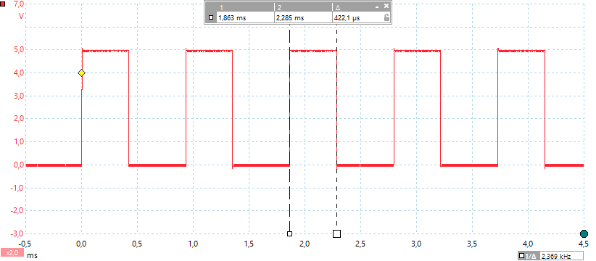

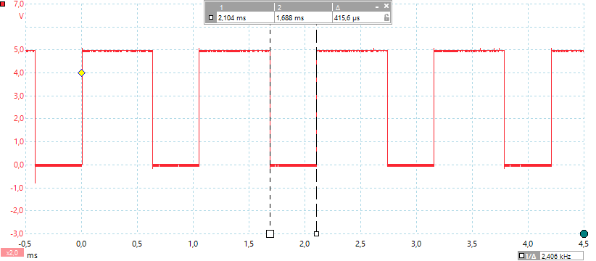

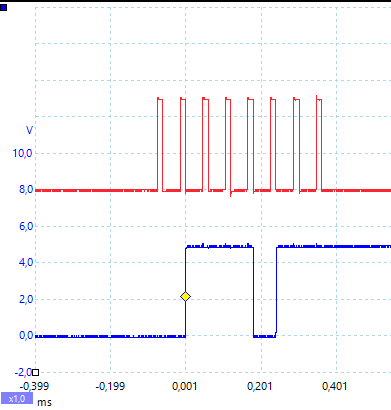

Die Polarität des Impulses ist immer invers zum Status des Pins vorher. Ist P1 LOW bewirkt ein Aufruf von PULSOUT einen HIGH-Impuls (Abb. 1); Polarität CPOL = 0. Mit P1 HIGH produziert PULSOUT einen LOW-Impuls; CPOL = 1 (Abb. 2).

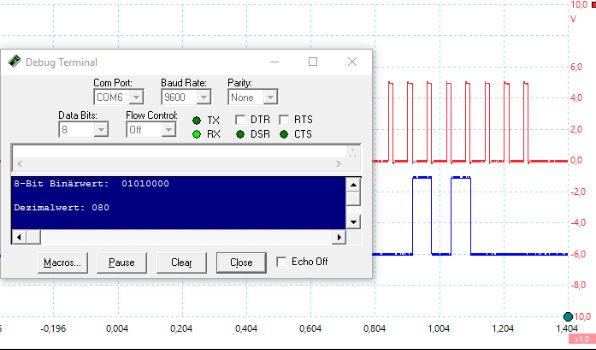

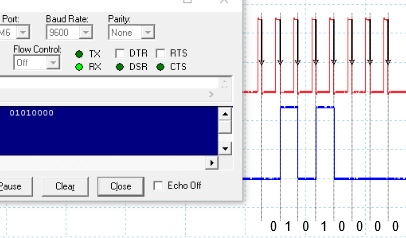

2 - CLK- und DATA-Signale

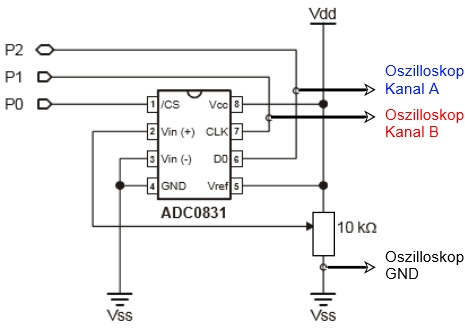

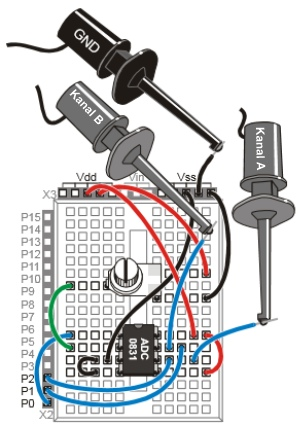

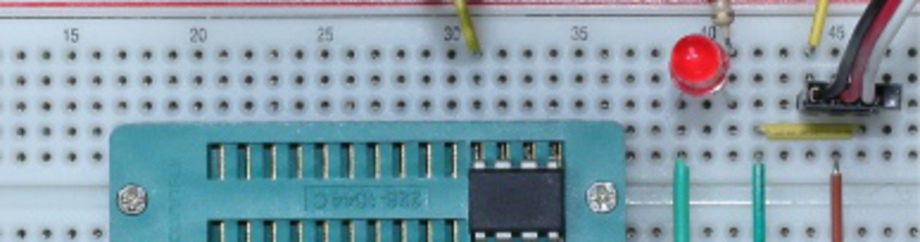

In dieser Übung wird eine A/D Wandler Schaltung mit dem Baustein ADC0831 aufgebaut. Die CLK- und DATA-Signale werden auf dem Oszilloskop sichtbar gemacht um zu zeigen, wie Daten vom A/D-Wandler zur BASIC Stamp übertragen werden. Wird der Drehknopf am Potenziometer verstellt, erkennt man die 8-Bit Werte, die vom ADC0831 übertragen werden.

| Material und Aufgaben zu CLK- und DATA Signale | |

| Material |

1x Board of Education mit BASIC Stamp 2 1x ADC0831 8-Bit A/D Wandler 1x 10kOhm Widerstand (braun-schwarz-orange) 14x Steckdraht |

| Aufgaben |

|

| Synchrone serielle Kommunikation sichtbar machen | |

| Aufgaben |

|

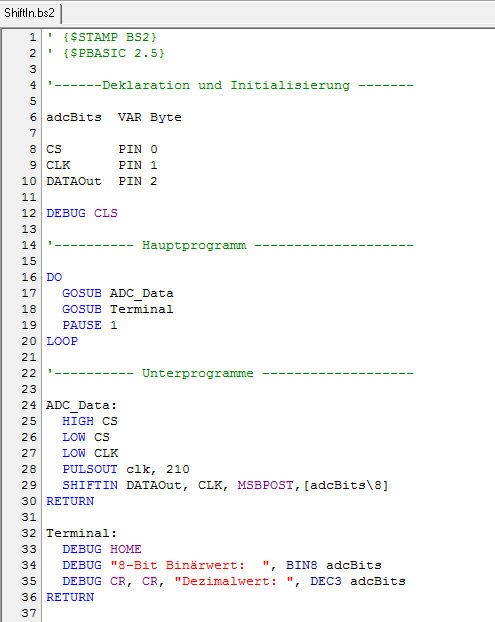

Das Programm ShiftIn.bs2

Wie arbeitet das Programm ShiftIn.bs2

Um verstehen zu können, wie das Programm arbeitet, schauen wir es etwas genauer an. Es besteht aus den drei Blöcken

-

Deklaration und Initialisierung -

Hauptprogramm -

Unterprogramme

Zeilen 5 - 12

Im Deklarations- und Initialisierungsteil werden die Größen mit sprechenden Namen benannt, die im weiteren Verlauf des Programms benötigt werden.

CS ist der ChipSelect (CS) Eingang des ADC0831 und mit dem I/O Port P0 der BASIC Stamp verbunden.

CLK ist der Clock-Eingang des ADC0831, er liegt an P1 und

DATAOut (DO, Pin 6 des Chip) an P2; über ihn liest die BASIC Stamp die konvertierten Daten des AD-Wandlers ein.

Zeilen 15 - 21

Im Hauptprogramm werden zwei Unterprogramme aufgerufen und eine Pause von 1ms ausgeführt. Das Wesentliche passiert also in den beiden Unterprogrammen.

Zeilen 24 - 30

Das Unterprogramm ADC_Data enthält zwei Befehle

-

PULSOUT -

SHIFTIN

die wir uns etwas genauer anschauen. PULSOUT ist bereits aus dem Kapitel 1 - synchrone serielle Kommunikation bekannt. Der SHIFTIN-Befehl ist neu.

Der Befehl SHIFTIN

Liest die Daten von einem synchronen seriellen Gerät aus. Der Befehlsaufruf lautet

- SHIFTIN DPin, CPin, Mode, [Variable{\Bits}, Variable

{\Bits}, ...]

DPin verbunden mit dem DataOut-Pin (D0) des seriellen Gerätes

CPin verbunden mit dem CLK-Pin (CLK) des seriellen Gerätes; wird in Modus OUTPUT

geschaltet

Mode 1 - MSBPOST Data msb-first

Variable Variable, in der die einlaufenden Daten abgelegt werden

Bits optional, Anzahl übertragender Bits (1 - 16); wenn nicht benannt, dann 8 Bits

Ein bisschen sollten wir uns jetzt über das SPI-Protokoll unterhalten, damit wir verstehen, was da in den beiden folgenden kurzen Programmzeilen abläuft.

3 - Serial Peripheral Interface (SPI)

Es handelt sich um ein Bussystem, das aus drei Leitungen besteht und der seriellen synchronen Datenübertragung zwischen zwei verschiedenen ICs dient. Der Bus besteht aus folgenden Leitungen

-

MOSI (Master Out -> Slave In) oder SDO (Serial Data Out) oder kürzer DO -

MISO (Master In -> Slave Out) oder SDI (Serial Data Input) oder kürzer DI -

SCK (Serial Clock) oder Schiebetakt CLK

Für jeden Slave wird eine Slave Select (SS) oder Chip Select (CS) Leitung benötigt. Über sie wird der Chip vom Master zur Kommunikation aufgefordert. Dies geschieht mit einer HIGH - LOW Signalfolge. Im Programm ShiftIn.bs2 sieht das wie folgt aus:

-

ADC_Data: HIGH_CS LOW_CS

Die beiden nachfolgenden Programmzeilen

-

LOW CLK PULSOUT CLK, 210

bewirken, dass der Takt im Ruhezustand auf LOW-Pegel liegt (CPOL = 0) und mit der ersten Flanke auf HIGH steigt und mit der zweiten fallenden Flanke auf LOW zurückgeht.

Die CLK-Phase bestimmt, bei welcher Flanke des Taktsignals die Daten übertragen werden. CPHA = 1 bedeutet, dass die Daten mit der zweiten fallenden Flanke übernommen werden.

Nach Vorgabe des Herstellers arbeitet der ADC0831 nach dem SPI-Übertragungsmodus CPOL = 0 (Takt im Ruhezustand auf LOW-Pegel) und CPHA = 1 (Daten werden mit der zweiten fallenden Flanke des Taktsignals übernommen).

Der Befehl

-

SHIFTIN DATAOut, CLK, MSBPOST, [adcBits\8]

verschiebt 8-Bit Datenworte aus dem ADC0831 DO-Pin in die Variable adcBits, in der Reihenfolge msb-first. Die BASIC Stamp steuert die CLK-Leitung, der ADC0831 die DATA-Leitung.

| Aufgaben |

|