Digitaltechnik - 5

5.1 - Frequenzteiler

Bei Frequenzteilern unterscheidet man

- asynchrone

- synchrone

Ihre Aufgabe besteht darin, eine vorgegebene Eingangsfrequenz f0 auf eine bestimmte Zielfrequenz f zu verringern. Dies geschieht technisch durch das Hintereinanderschalten von Flipflops, wobei jedes FF die Eingangsfrequenz halbiert (f = f0 /2).

Allein mit dem Hintereinanderschalten von Flipflops lassen sich Eingangsfrequenzen nur geradzahlig teilen: f aus {f0/2, f0/4, f0/8, …, f0/2n }. Über entsprechende Reset-Bedingungen lassen sich aber auch beliebige andere Teiler finden.

Das Verhältnis von Ausgangs- zu Eingangstakt gibt das Frequenzverhältnis an. Wenn auf zwei Eingangstakte ein Ausgangstakt kommt, liegt ein Frequenzverhältnis von 1 : 2 vor.

Der einfachste Flipfloptyp für einen Frequenzteiler ist das JK-Flipflop.

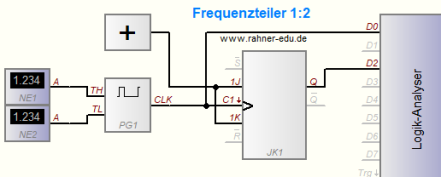

5.2 - Geradzahliger Frequenzteiler 1 : 2

Mit einem JK-Flipflop lässt sich eine Eingangsfrequenz f0 im Verhältnis 1 : 2 herunterteilen. Dazu müssen die Eingänge J und K verbunden und auf 1 oder HIGH gezogen werden. Das JK-Flipflop arbeitet dann wie ein T-Flipflop (Toggle-Flipflop).

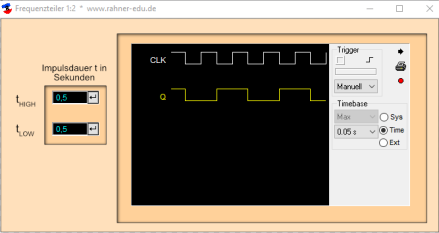

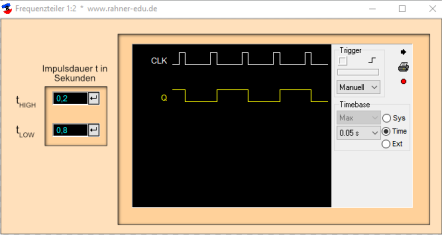

Das Impulsdiagramm dieses Frequenzteilers zeigt Abb. 2.

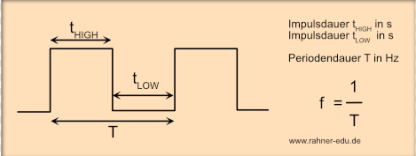

tHIGH gibt die Impulsdauer des Eingangsimpulses im Zustand HIGH oder 1 an; tLOW entsprechend für den Zustand LOW oder 0. Im vorliegenden Fall ist das Tastverhältnis 50%.

Verändert man das Tastverhältnis, bleibt dies ohne Auswirkung auf den Ausgang (s. Abb. 3), da sich die Periodendauer nicht verändert hat.

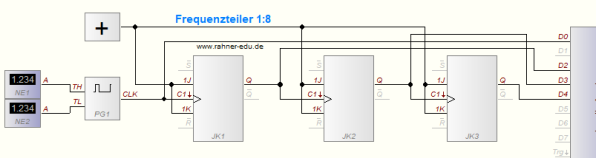

5.3 - Geradzahliger Frequenzteiler 1 : 2N

Wie bereits an anderer Stelle geschrieben, lassen sich alle geraden Frequenzteiler durch Hintereinanderschalten von N (natürliche Zahl > 0) JK-Flipflops realisieren.

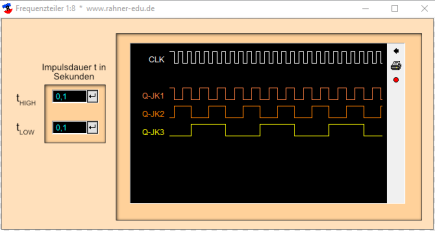

Das soll an einem Frequenzteiler 1 : 8 -> 1 : 23 exemplarisch gezeigt werden. Dazu sind drei JK-Flipflops hintereinander zu schalten.

Wie arbeitet die Schaltung?

Die Eingangsfrequenz liegt, da tHIGH und tLOW beide auf 0,1s eingestellt sind bei 5 Hz (für Hinweise siehe Abb. 6).

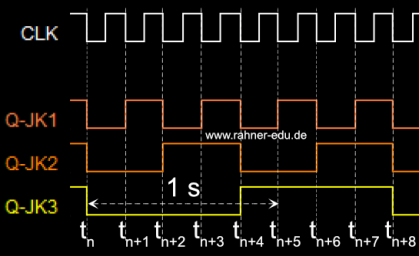

Die oberste Zeile CLK im Oszillogramm (s. Abb. 7) zeigt eine Eingangsfrequenz von 5 Hz oder T = 0,2s. Am Ausgang des ersten JK-Flipflops (Q-JK1) werden 2,5 Hz oder T = 0,4 s gemessen, am Ausgang des zweiten JK-FF (Q-JK2) 1,25 Hz oder 0,8 s und am Ausgang Q-JK3 0,625 Hz oder 1,6 s.

Wie dem Schaltungsaufbau zu entnehmen ist, wird nur das Flipflop JK1 vom Taktgeber angesteuert; das FF JK2 erhält seinen Taktimpuls von JK1 und JK3 von JK2. Sie werden asynchron angesteuert.

Zu einem bestimmten Zeitpunkt tn sind die Ausgänge an allen Flipflops 0 oder LOW. Bei tn+1 und fallender Flanke an CLK geht Q-JK1 auf HIGH, JK2 und JK3 reagieren nicht; sie reagieren nur auf eine fallende Flanke.

Mit der nächsten fallenden Flanke an CLK bei tn+2 fällt auch die Flanke an Q-JK1, was zur Folge hat, dass Q-JK2 auf HIGH oder 1 geht.

Die nächste fallende Flanke an CLK beeinflusst nur Q-JK1, es geht auf HIGH (tn+3). Die fallende Flanke bei tn+4 bewirkt, dass Q-JK1 und Q-JK2 auf LOW gezogen werden; damit geht Q-JK3 auf HIGH.

Die Vorgänge setzen sich weiter fort, bis bei tn+8 alle Flipflops wieder auf LOW zurückgesetzt sind.

Bleibt zum Schluss die Frage, wieviele JK-Flipflops man hintereinander schalten kann oder anders ausgedrückt: "Wie hoch ist die Grenzfrequenz eines Frequenzteilers?".

Maximale Arbeitsfrequenz

Jedes Flipflop hat eine Verzögerungszeit. Ein Blick in die Datenblätter der entsprechenden JK-Flipflop Bausteine zeigt: die liegt i.a. zwischen 20 und 50 ns. Bei zehn Flipflops läge die Verzögerungszeit dann zwischen 100 und 500 ns oder 0,1 bis 0,5 µs und die maximale Arbeitsfrequenz dann zwischen 10 und 20 MHz.

Bis jetzt haben wir nur geradzahlige Frequenzteiler betrachtet. Bei ungeradzahligen Teilern nimmt man den Rückstelleingang am Flipflop zu Hilfe. Wie das geht, zeigt der folgende Abschnitt.

5.4 - Ungeradzahliger Frequenzteiler 1 : 3

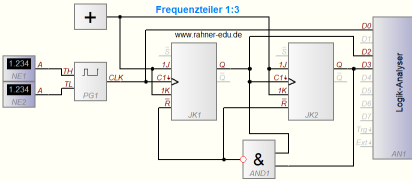

Bei einem ungeradzahligem Teilungsverhältnis setzt man ein AND-Gatter für die automatische Rückstellung (RESET) ein.

Das zugehörige Oszillogramm zeigt, dass die Ausgangsfrequenz 2 Hz ist.

Wie arbeitet die Schaltung?

Aus den vorherigen Überlegungen wissen wir, dass das erste Flipflop JK1 mit seiner fallenden Flanke beim Nachbar-Flipflop JK2 dafür sorgt, dass dessen Ausgang Qn auf Qn+1 geht. Gestartet wird bei tn mit dem Zustand CLK = Q-JK1 = Q-JK2 = 0.

|

Zeit |

Q-JK1 1-er |

Q-JK2 2-er |

|

tn |

0 |

0 |

|

tn+1 |

1 |

0 |

|

tn+2 |

0 |

1 |

|

tn+3 |

1 |

1 |

|

tn+4 |

0 |

0 |

Nacheinander werden die Phasen

- {Q-JK1 = 1, Q-JK2 = 0}, {Q-JK1 = 0, Q-JK2 = 1} und {Q-JK1 = 1, Q-JK2 = 1}

durchlaufen. Zum Zeitpunkt tn+3 werden die beiden JK-Flipflop über das AND-Gatter zurückgesetzt und der Zählvorgang beginnt sofort von vorn. Der RESET-Impuls ist so kurz, dass er auf der Zeitachse in diesem Maßstab nicht angezeigt werden kann; es folgt sofort tn+4. Aus diesem Grund habe ich die Zeitpunkte zusammengelegt zu tn+3/4.

Zusatzaufgaben

- Die Frage, aus wievielen JK-Flipflops ein Frequenzteiler 1 : 5 aufgebaut und mit welcher Zusatzbeschaltung er versehen sein müsste, sollte sich jetzt beantworten lassen. Überlege selbst und gib eine Schaltungslösung an.

- Entwirf einen Schaltungsaufbau für einen Teiler 1 : 6.

- Entwirf einen Schaltungsaufbau für einen Teiler 1 : 7.

6 - Zähler

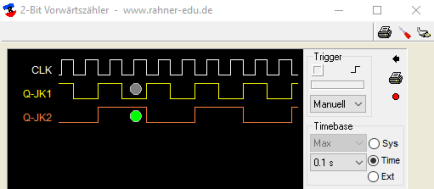

6.1 Asynchroner 2-Bit Vorwärtszähler

Zähler sind Schaltungen, die eine Impulsfolge, die an ihrem Eingang anliegt, abzählen und zwischenspeichern. Sie können als Vor- oder Rückwärtszähler konzipiert sein oder beide Modi zulassen, die dann umschaltbar sind.

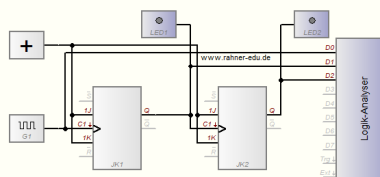

Wie bei den Frequenzteilern spricht man von asynchronen Zählern, wenn der Ausgang des ersten Flipflops den Takteingang des nachfolgenden Flipflops ansteuert. Das ist bei der folgenden Schaltung der Fall.

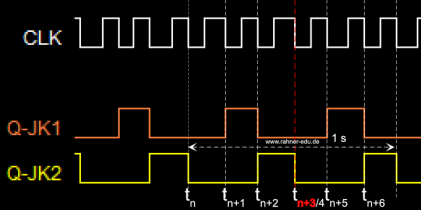

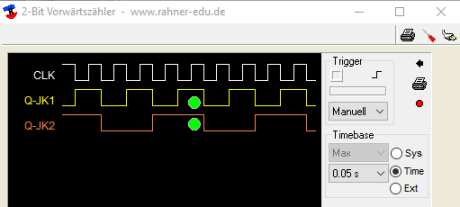

Dem Impuls- oder Zeitdiagramm lassen sich die vier binären Zählzustände entnehmen. Die beiden LEDs stehen im Diagramm an der Stelle Q-JK1 = HIGH, Q-JK2 = HIGH.

6.2 Asynchroner 2-Bit Rückwärtszähler

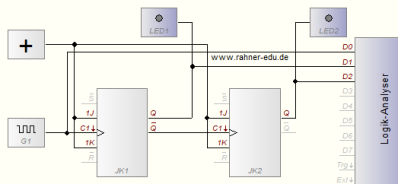

Ein Rückwärtszähler unterscheidet sich von einem Vorwärtszähler nur dadurch, dass der negierte Ausgang Q´-JK1 vom ersten Flipflop mit dem Eingang des zweiten verbunden ist.

Zeitdiagramm

Im Zeitdiagramm erkennt man links neben den LEDs den Zustand Q-JK1 = Q-JK2 = 1 oder 310. Mit der ersten fallenden Flanke an CLK wird Q-JK1 auf LOW oder 0 gezogen, während Q-JK2 auf HIGH oder 1 verbleibt. Dies entspricht der Dezimalzahl 2.

Mit der folgenden fallenden Taktflanke an CLK geht Q-JK1 auf HIGH und Q-JK2 bleibt auf LOW. Dies entspricht 110. Die nächste fallende Taktflanke zieht die Ausgänge Q von beiden Flipflops auf 0.

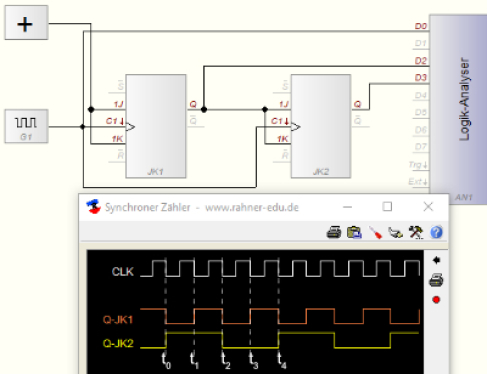

6.3 - Synchroner 2-Bit Vorwärtszähler

Das JK-Flipflop setzt seine Ausgänge nur bei fallender Taktflanke am CLK-Eingang. Ist Eingang 1J auf HIGH, wird das Flipflop gesetzt; bei einem HIGH an 1K wird es zurückgesetzt. Sind beide Eingänge 1J und 1K auf HIGH oder 1, toggelt das Flipflop bei jeder fallenden Flanke seinen Ausgang Q.

Wie arbeitet die Schaltung?

- Die beiden Eingänge von JK1 liegen schaltungsbedingt immer auf 1, d.h., das Flipflop kehrt bei jeder fallenden Taktflanke seinen Ausgangszustand um: aus HIGH wird LOW und umgekehrt.

- Zur Zeit t0 ist Q-JK1 LOW, dann liegen auch die Eingänge von JK2 auf LOW und Q-JK2 ist HIGH.

- Ein fallender Taktimpuls an JK2 (t1) hat keine Wirkung auf seinen Ausgang; der Zustand bleibt erhalten. JK1 wechselt aber in den Zustand Q-JK1 = HIGH und damit sind beide Eingänge von JK2 ebenfalls 1.

- Die nächste fallende Flanke (t2) zieht Q-JK1 auf LOW; JK2 toggelt in den Zustand Q-JK2 = LOW und ändert bei der nächsten fallenden Taktflanke (t3) seinen Ausgangszustand nicht. Das geschieht erst wieder bei t4.